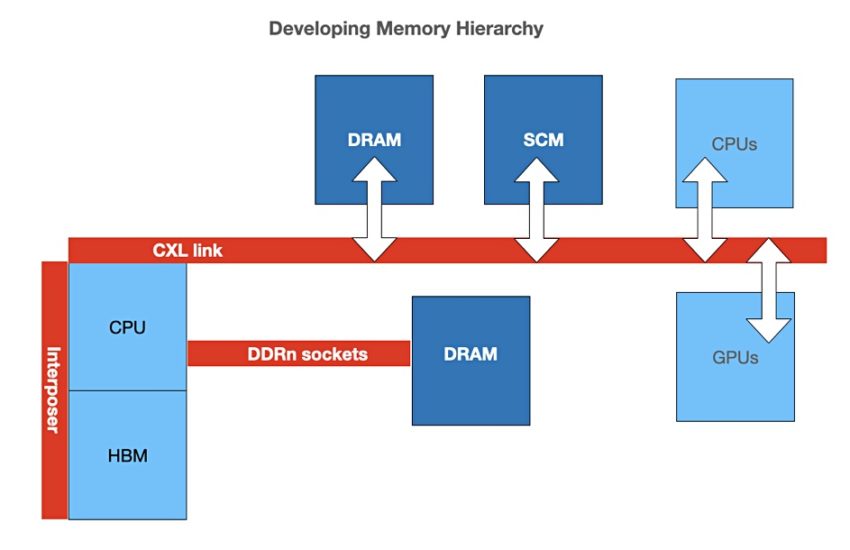

本文探讨了使用廉价闪存内存(flash memory)在新型互连技术(如CXL)上以应对“内存墙”的可行性。我们探索了CXL启用的闪存设备的设计空间,并展示了缓存和预取等技术可以帮助缓解有关闪存性能和寿命的担忧。

继续阅读

Google AI TPU

本文探讨了使用廉价闪存内存(flash memory)在新型互连技术(如CXL)上以应对“内存墙”的可行性。我们探索了CXL启用的闪存设备的设计空间,并展示了缓存和预取等技术可以帮助缓解有关闪存性能和寿命的担忧。

继续阅读

Compute Express Link(CXL)是一种高带宽、低延迟的CPU与设备之间的互连标准,它构建在现有的PCI Express(PCIe)基础设施之上,充分利用了PCIe的物理和电气接口,并引入了额外的传输协议。

继续阅读

PCI(Peripheral Component Interconnect)是现代计算机中外围设备互连的标准,涵盖了从便携设备到数据中心和高性能计算等各种领域。

继续阅读

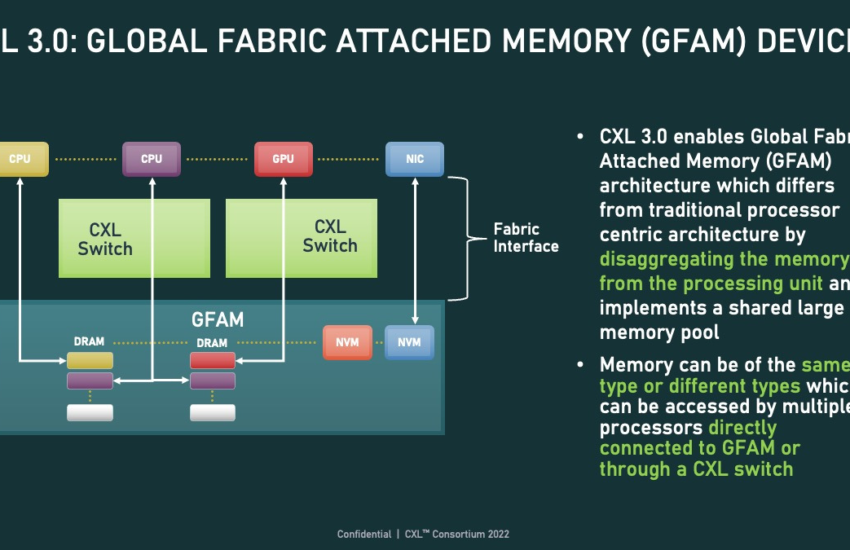

CXL 3.0允许每个主机支持多达16个加速器,使其成为用于GPU的标准一致性互连。它还增加了点对点(P2P)通信、多级交换和最多4,096个节点的结构。

继续阅读

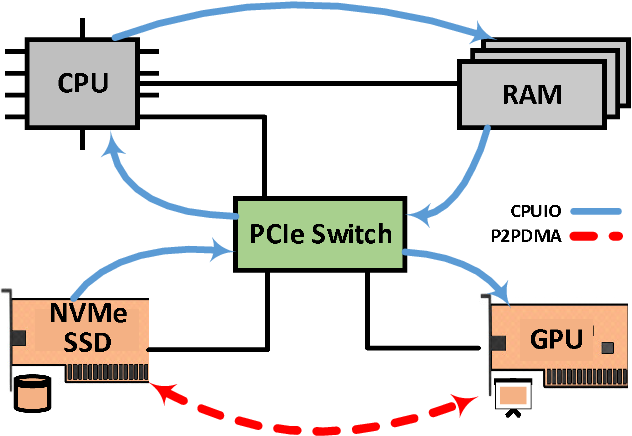

在2023年“Linux存储、文件系统、内存管理和BPF峰会”的首日全体会议上,Stephen Bates主持了一场关于“点对点DMA(P2PDMA)”的讨论。这个想法的核心在于,从一个连接了PCIe的设备向另一个设备传输数据时,消除主机系统的介入。

继续阅读

不管你是否考虑使用卸载卡、SmartNIC、GPU、DPU还是SPU,有一点是肯定的,它们并非都是相同水平的。

继续阅读

新一代应用程序和工作负载,如AI/DL和HPC,正在打破传统存储基础设施模型和框架的界限。

继续阅读

根据负责该标准的组织的最新公告,PCI-Express 互连标准可能会在未来几年经历一些重大变化。

继续阅读

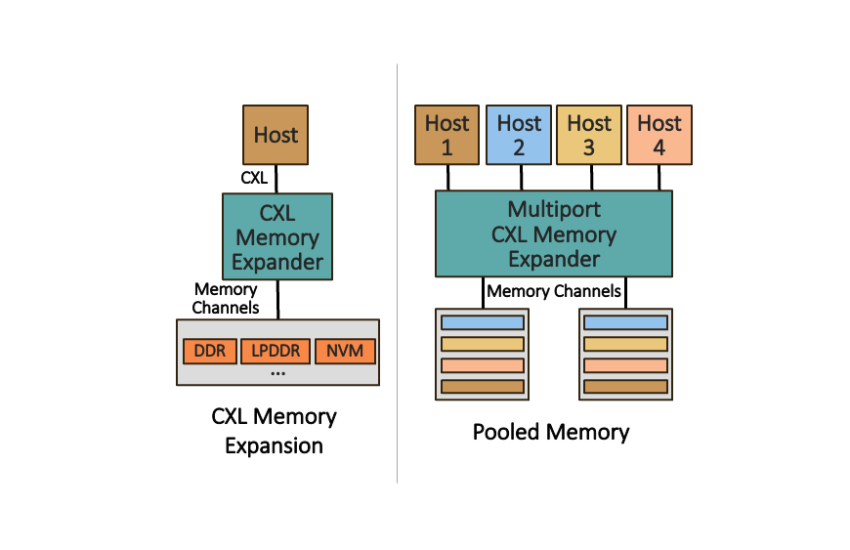

CXL 2.0将实现内存池技术,这听起来很棒,但具体容量有多大还有点模糊。内存池能容纳多少数据呢

继续阅读