供应商和JEDEC正在推进HBM4计划,因为他们怀疑新一代AI热潮意味着即将推出的英伟达GPU将更快地需要它。

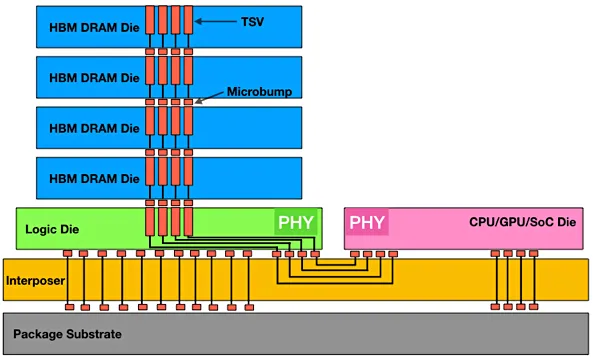

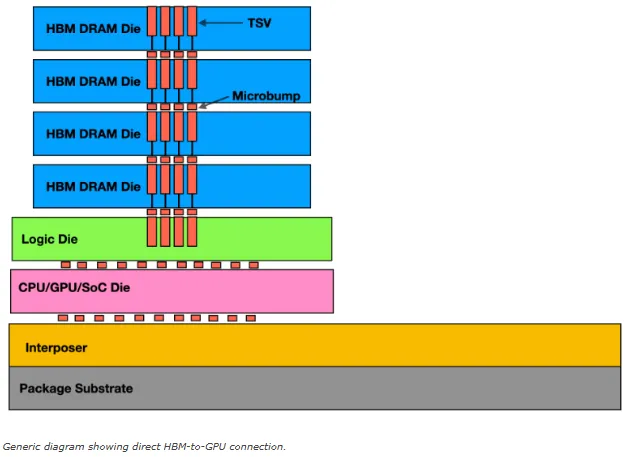

HBM(高带宽内存)绕过X86 socket连接的DRAM容量和带宽限制,将内存封装堆叠在逻辑层的顶部,并通过相互连接的TSV通道,将所有组件链接到GPU。JEDEC(Joint Electron Device Engineering Council)确认并发布HBM标准,目前是其第五个标准——HBM3E。

主要的HBM供应商是SK海力士,其次是三星,然后是美光。今年4月,由于英伟达对HBM芯片的需求,SK海力士2024年第一季度的收入飙升了144%。英伟达将HBM芯片与其GPU一起封装。TrendForce表示,在价格溢价和AI芯片需求增加的推动下,HBM市场有望实现“强劲增长”。

美光正在制造24GB的HBM3e芯片,配备8*3GB的堆叠DRAM芯片(8-high),供英伟达在其H200 Tensor核心GPU中使用。它还有一个12-high的设备,容量为36GB,性能超过1.2 TBps。三星也有自己的12-high 36GB HBM3e设备,带宽高达1.28 TBps。

JEDEC表示将在今年年底发布完整的HBM4规格(几个月前的时间表是2025年交付)。HBM4的初步特征已经显现出来。

HBM4控制器将能够控制HBM3E DRAM。HBM3E芯片具有1024位宽的通道,HBM4将其加倍到2048位。采用HBM3E堆叠的DRAM芯片最多可达12。HBM4增加了三分之一,达到16层,同时支持24Gb和32Gb层。这将提升容量,最高支持512 Gb (64GB),带宽高达6.4 GTps,这意味着主机GPU可以更快地获得更多数据,从而处理更大的大型语言模型(LLM)。

16-high的堆叠明显高于12-high的堆叠,JEDEC正在考虑将HBM芯片的最大高度参数从720um提高到775um。降低高度的一种方法是采用更小的工艺节点。

台积电和SK海力士最初计划使用12nm的12FFC+工艺,但现在打算增加5nm的N5工艺技术。三星表示,其HBM4逻辑芯片将采用4nm工艺,与HBM3E芯片使用的10nm工艺相比,这将提高芯片的性能并降低功耗。

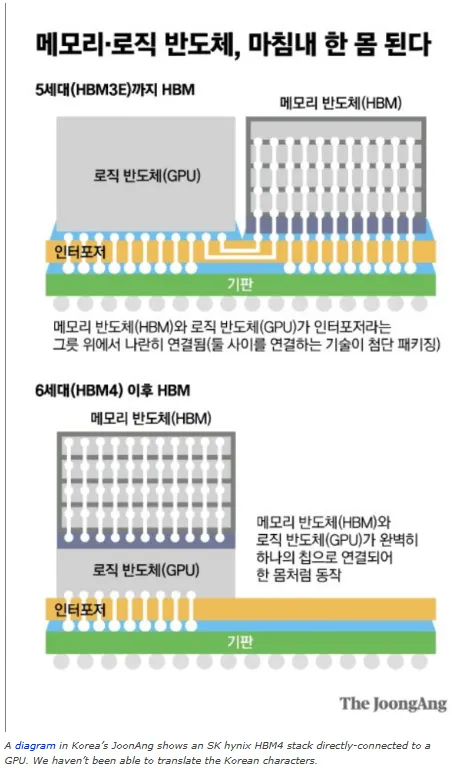

一个直接的HBM到GPU的连接,不需要中间层组件,将缩短DRAM和GPU之间的距离,加快数据访问。然而,热设计限制可能会阻止HBM4堆栈直接绑定到GPU。两个温度较高的设备会使设备难以冷却。

无论这些问题的结果如何,我们都可以相信:SK海力士,三星和美光之间的激烈竞争将生产出具有HBM4的GPU系统,更快地访问更多内存,并使Gen AI LLM开发成本更低,进而扩展到更大的模型。