距离Intel Xeon Ice Lake处理器发布只有短短的几个月时间,而且Intel将全面转向PCIe Gen4平台,但PCIe Gen4将是一个相对较短时间段的互联方案,即使AMD,ARM和IBM POWER9都将支持该标准一段时间。业界现在反而更期待PCIe Gen5,它会有效地将速度提高一倍,同时也进去了CXL时代(CXL在PCIe Gen5之上运行)。我们现在已经开始看到PCIe Gen5生态系统产品的发布了,包括Microchip Switchtec PCIe 5.0的交换机。

Microchip Switchtec PCIe 5.0 Switches

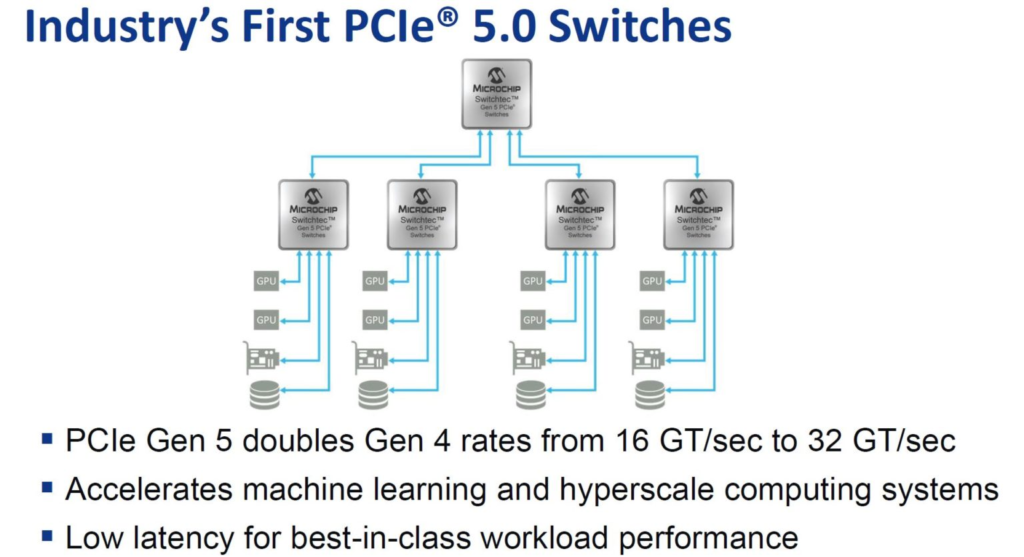

Microchip Switchtec PCIe 5.0交换机系列产品正在尝试在PCIe Gen5推出前就发布。PCIe交换机有效地允许PCIe端点具有一种通信结构,在某种方式上,与你办公室(或在当前环境下的家庭办公室)中使用的以太网交换机非常类似。

向PCIe Gen5迁移的原因很简单,我们可以获得的速度是PCIe Gen4的两倍。例如,在Intel Xeon平台上,我们于2012年首次看到了带有PCIe Gen3的Xeon E5-2600 V1代的产品。九年后,作为计算机体系结构中的永恒,英特尔普遍可用的Xeon产品仍然只支持PCIe Gen3。 同时,我们已经看到行业从10/40GbE过渡到了25/100/200/400GbE,从硬盘驱动器到NVMe存储,用于计算的海量GPU的出现,以及从8核CPU到64核和80核设计,以及更大的芯片,PCIe Gen3成为通信的主要瓶颈,因此行业需要加快节奏。

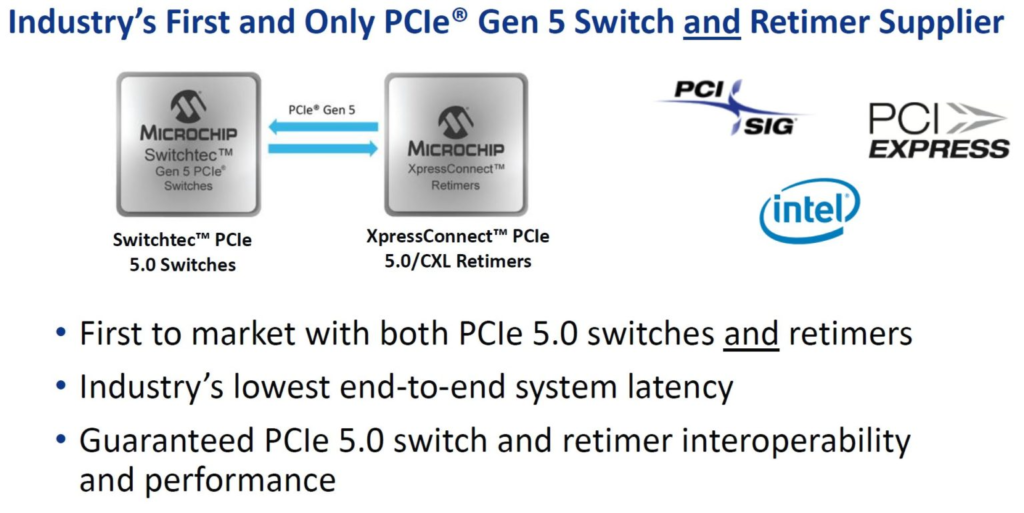

我们之前介绍了2020年推出的Microchip XpressConnect PCIe Gen5和CXL 2.0 Retimer,新的Switchtec PCIe Gen5交换机旨在与这些Retimer一起使用,我们问Microchip,得到的回复是这些新Switch暂时不支持CXL。

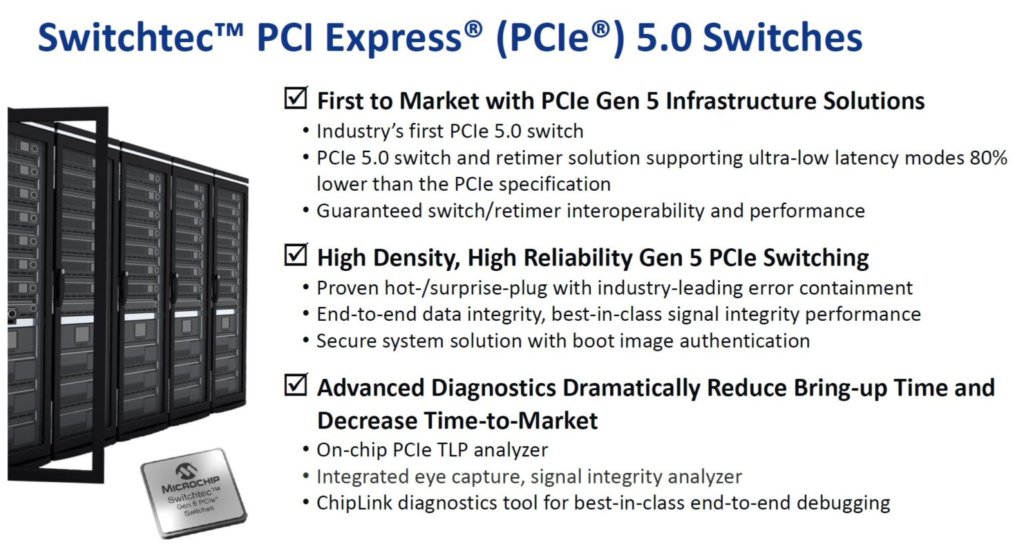

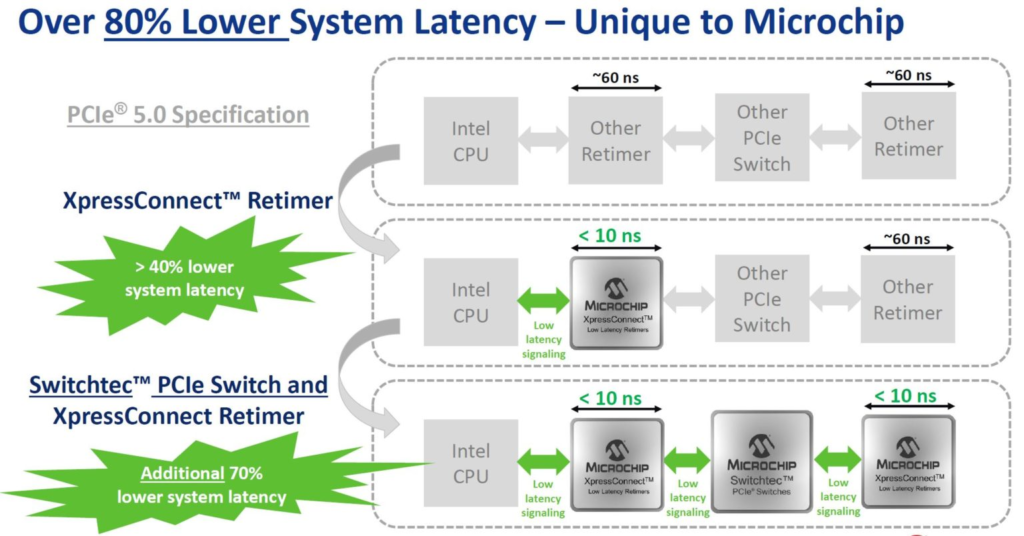

Microchip的解决方案的跃点延迟小于10ns,与Intel合作,实现比PCIe Gen5规范规定的约60ns更低的系统延迟。 英特尔正在与PCIe Gen5生态系统的合作伙伴进行合作,因为PCIe Gen4生态系统将为时已晚。我们看到Intel在PCIe Gen4上进行投资,与已经提供了PCIe Gen4有一段时间的其他供应商实现了一样的功能。 我们认为Intel在PCIe Gen5上的投资是超越了一步。 Intel可以与Microchip合作,创建一条每个步骤的延迟都较低通信链路,我们还没有看到的是终端设备,但Microchip现在展示的关键是创建了较低延迟的链路,因为每个跃点都可能会增加延迟。

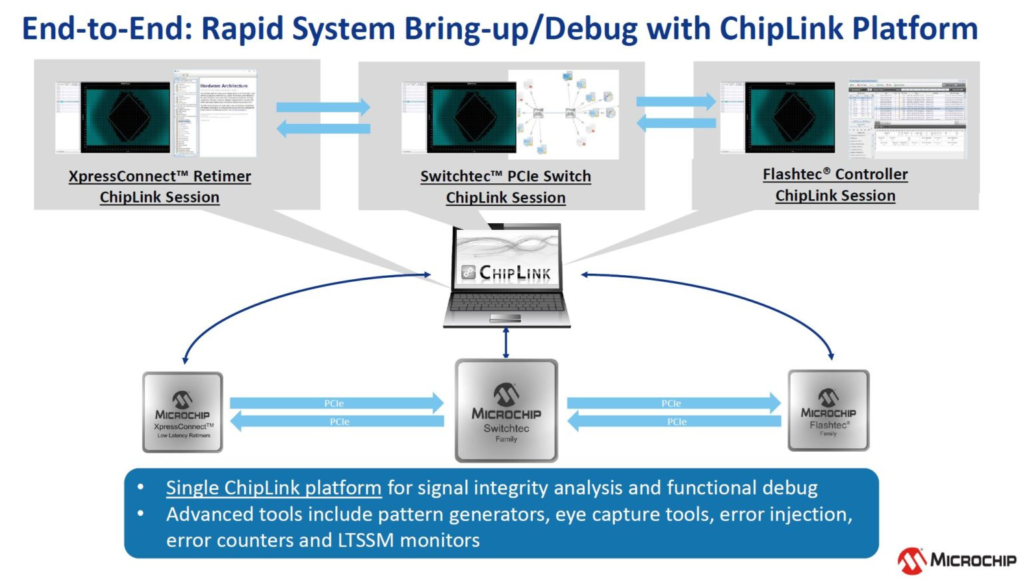

作为围绕PCIe的行业节奏不断增强的一部分,系统设计师没有像我们在PCIe Gen3中看到的那样拥有近十年的奢侈品。 取而代之的是,系统将需要更快地上线,这意味着存储磁盘架,多GPU产品以及其他常见的PCIe交换机拓扑将需要更快地通过设计和验证周期。Microchip有ChipLink可以帮助完成该过程。对于终端用户来说,这似乎并不令人兴奋,但是对于那些设计由这些组件组成的产品的人来说,能够从PCIe交换机和Retimer中获取数据有助于加快验证速度。

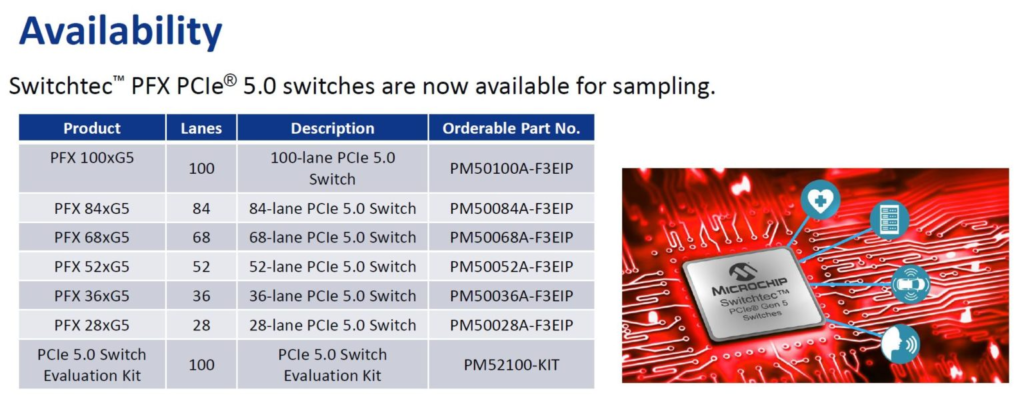

SKU范围从28到100通道的配置。除了最小的28通道设计外,可能你注意到的36到100通道的设计实际上是Z * 16 + 4。PCIe x16通道很常见,因此尽管SKU可以支持分叉成较小的链接,但它们的设计是围绕它们的倍数进行的。我们被告知额外的四个通道仍在相同的交换机交叉开关结构上,但是是为希望以额外的通道进行连接的客户添加的,比如连接到BMC(管理控制器)。必须记住,PCIe Gen5 x4通道大致等于PCIe Gen3 x16插槽的带宽。

在可用性方面,该交换芯片现在已经开始打样,远远超前了将在2022年可能推出的PCIe Gen5。

小结

很高兴看到行业逐渐向PCIe Gen5迈进。 对于更广泛的行业,重要的是Microchip能够领先于系统设计周期,以提供Broadcom PLX交换机系列产品的替代产品。购买PLX系列产品时,PCIe交换机价格大幅上涨,这在早期影响了NVMe的推广和使用,在市场上拥有强大的第二资源很重要。