本指南提供了第五代AMD EPYC™9005系列处理器内部IP的高级技术概述。

第1章:简介

AMD EPYC™9005系列处理器代表了第五代AMD EPYC服务器级处理器。这代AMD EPYC处理器采用AMD最新的“Zen 5”计算核心、下一代I/O芯片、增强的安全功能以及更高的内存和I/O带宽和速度,同时使用现有的SP5插槽/封装。

一般规格

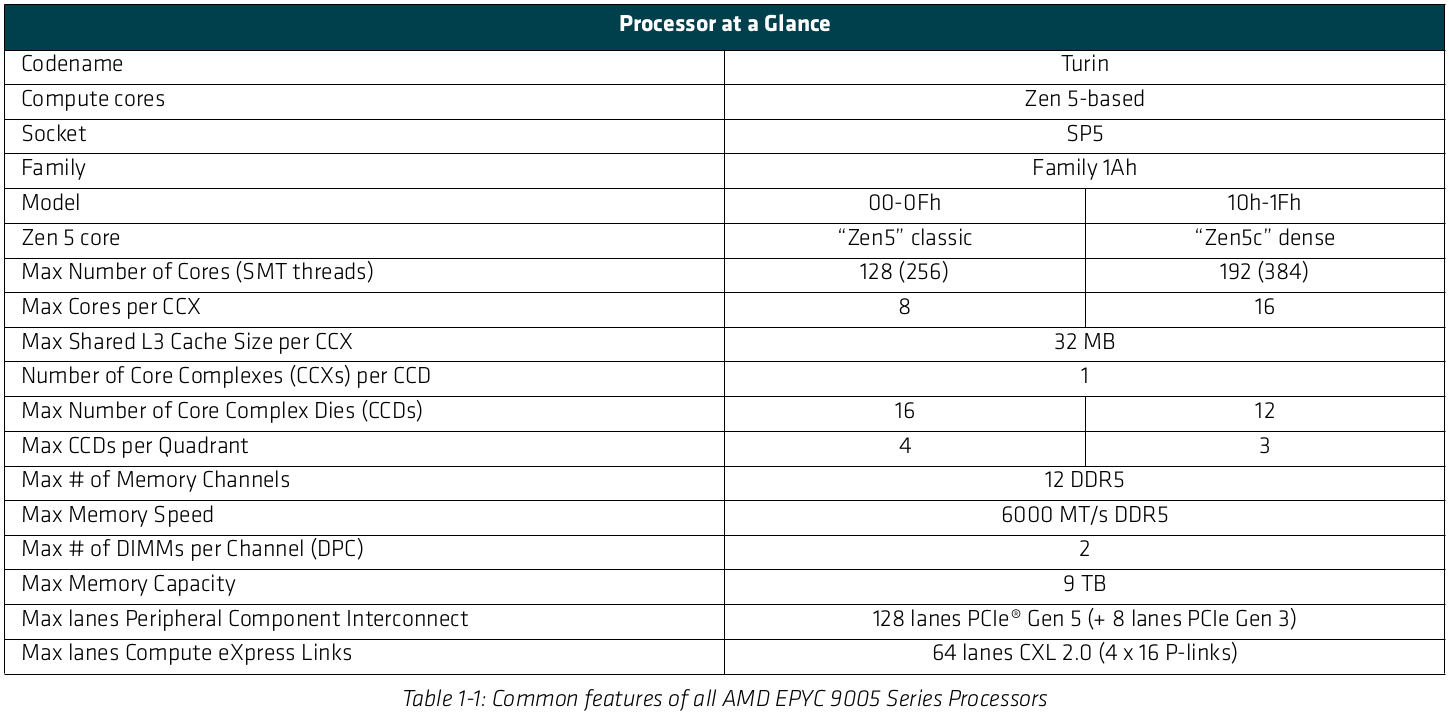

AMD EPYC 9005系列处理器提供多种配置,具有不同数量的核心、热设计点(TDP)、频率、缓存大小等,可补充AMD现有的服务器产品组合,进一步提高性能、能效和价值,适用于各种环境和工作负载。表1-1重点介绍了AMD EPYC 9005系列处理器的一些功能。

操作系统

AMD建议使用最新可用的目标操作系统版本和更新。请参阅AMD EPYC™ 处理器最低操作系统(OS)版本,了解详细的操作系统版本信息。

第2章:AMD EPYC™9005系列处理器

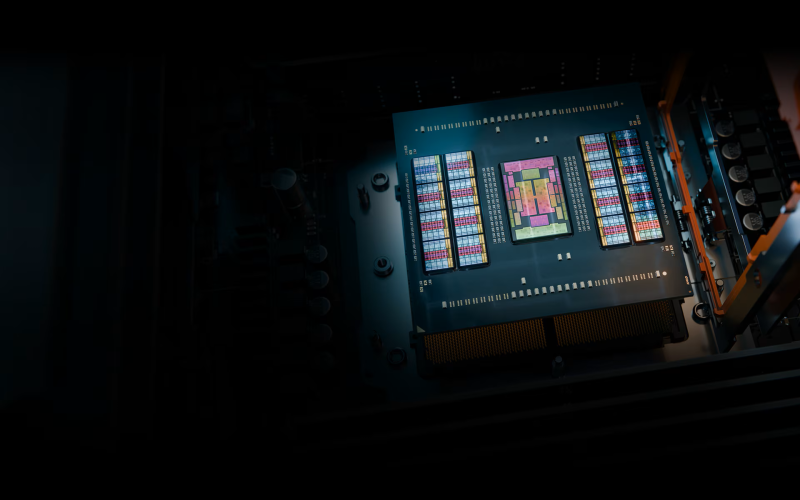

AMD EPYC 9005系列处理器将计算核心、内存控制器、I/O控制器、RAS(可靠性、可用性和可维护性)和安全功能集成到集成的片上系统(SoC)中。AMD EPYC 9005系列处理器保留了之前成功的AMD EPYC处理器经过验证的多芯片模块(MCM)芯片架构,同时对SoC组件进行了进一步改进。

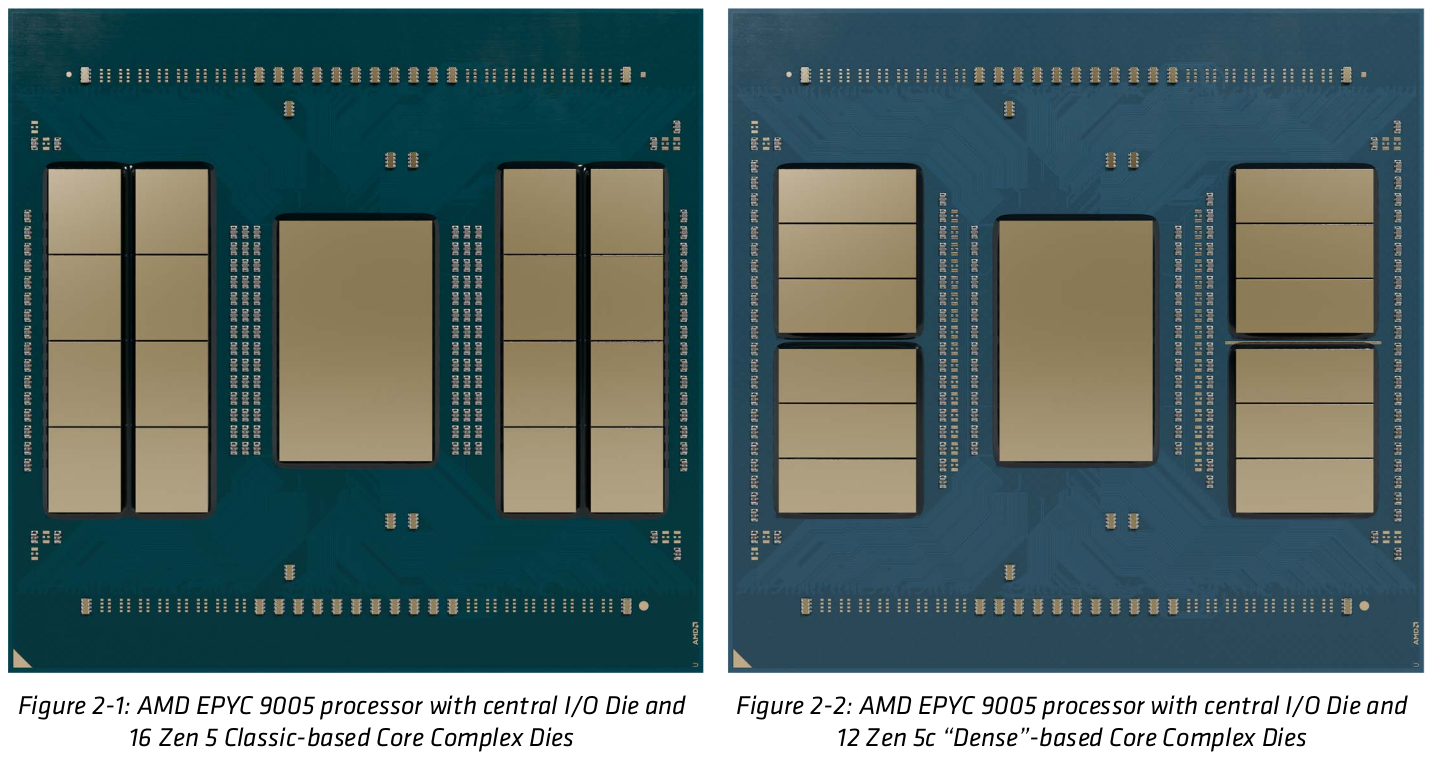

SoC包括核心复合体芯片(CCD),其中包含核心复合体(CCX),其中包含基于“Zen 5”的核心。CCD环绕中央高速I/O芯片(并通过Infinity Fabric互连)。以下部分介绍了每个组件。

“Zen 5” 核心

AMD EPYC 9005系列处理器基于全新“Zen 5”计算核心。与上一代“Zen”核心相比,“Zen 5”核心旨在提供每周期指令数(IPC)提升和频率改进。这包括对核心各个部分的多项增强,例如改进的分支预测和缓存效率。

每个核心的缓存包括:

- 高达32 KB的8路L1 I缓存(64个TLB条目)和48 KB的12路L1 D缓存(96个TLB条目)

- 高达1MB的私有统一16路L2缓存。所有缓存都使用64B缓存行大小。

每个核心都支持同步多线程(SMT),允许2个独立的硬件线程独立运行,共享相应核心的L2缓存。系统中的所有核心要么启用SMT运行,要么全部以单线程模式运行。这通常可通过系统BIOS选择。

所有AMD EPYC 9005系列处理器均兼容ISA。

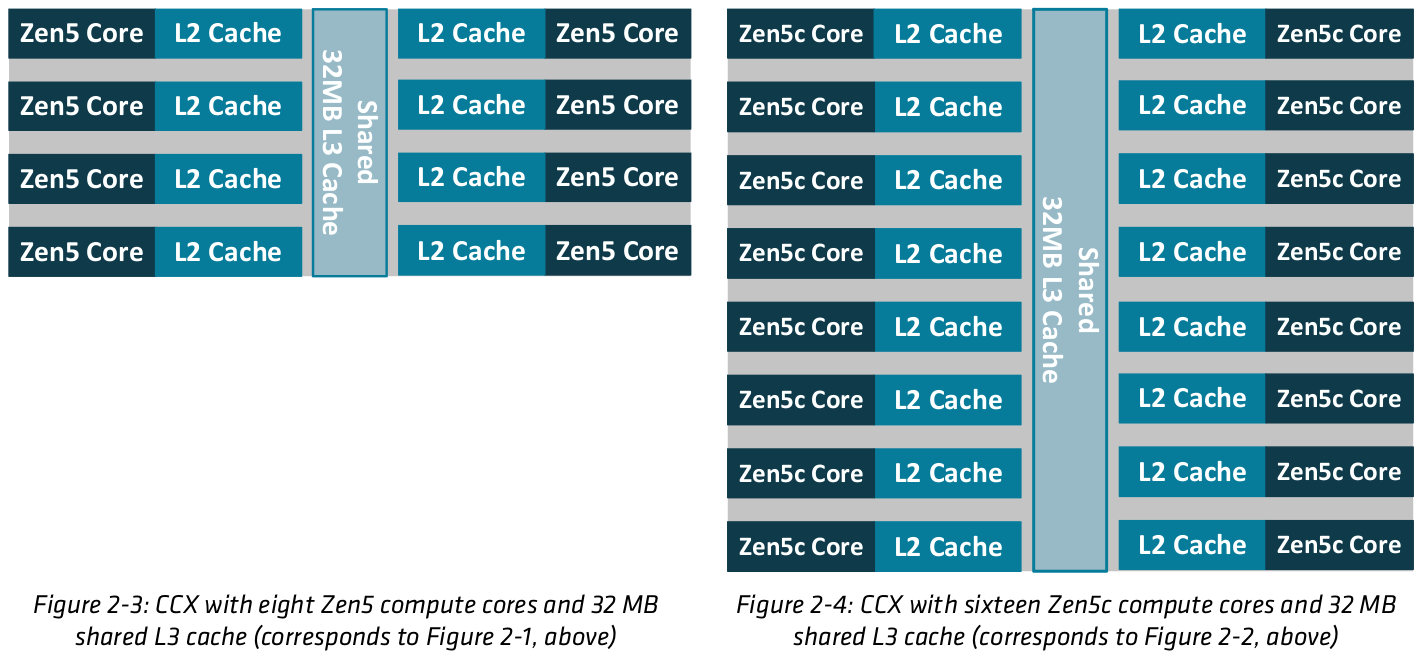

核心复合体(CCX)

术语“核心复合体”是指一组共享末级(L3)缓存的核心。AMD EPYC 9005 CCX最多可拥有八个Zen5(经典)或十六个Zen5c(密集)核心,共享32MB L3缓存。启用SMT可让单个CCX支持两倍于此数量的并发硬件线程,即16个或32个。

核心复合芯片(CCD)

AMD EPYC 9xx5系列处理器的每个核心复合芯片(CCD)都包含一个CCX。可以使用以下一种或两种方法在BIOS中禁用核心:

- 减少每个CCD的核心数量,同时保持CCD数量不变。此方法增加了每个核心的有效L3缓存比率,但减少了共享L3缓存的核心数量。

- 减少活动CCD数量,同时保持每个CCD的核心数量不变。此方法保留了核心之间缓存共享的优势,同时保持相同的每个核心缓存比率。

I/O芯片(Infinity Fabric™)

CCD通过I/O芯片(IOD)连接到内存、I/O和彼此的CCx。此中央AMD Infinity Fabric™ 提供数据路径和控制以互连CCX、内存和I/O。每个CCD通过专用的高速全局内存互连(GMI)链路连接到IOD。IOD有助于保持缓存一致性,此外还提供接口以通过其xGMI或G链路将数据结构扩展到潜在的第二个处理器。AMD EPYC 9005系列处理器支持最多4个xGMI (G链路),速度高达32Gbps。除了全局内存互连(GMI)链路以及PCIe® Gen5和CXL 2.0通道之外,IOD还通过P链路公开DDR5内存接口。

所有芯片(小芯片)通过AMD Infinity Fabric技术相互互连。每个CCD通过其自己的GMI连接连接到IOD。IOD提供最多12个支持DDR5内存的统一内存控制器(UMC)。IOD还提供4个“P-link”,系统OEM/平台设计人员可以配置这些“P-link”以支持各种I/O接口,例如PCIe Gen5和/或CXL 2.0。

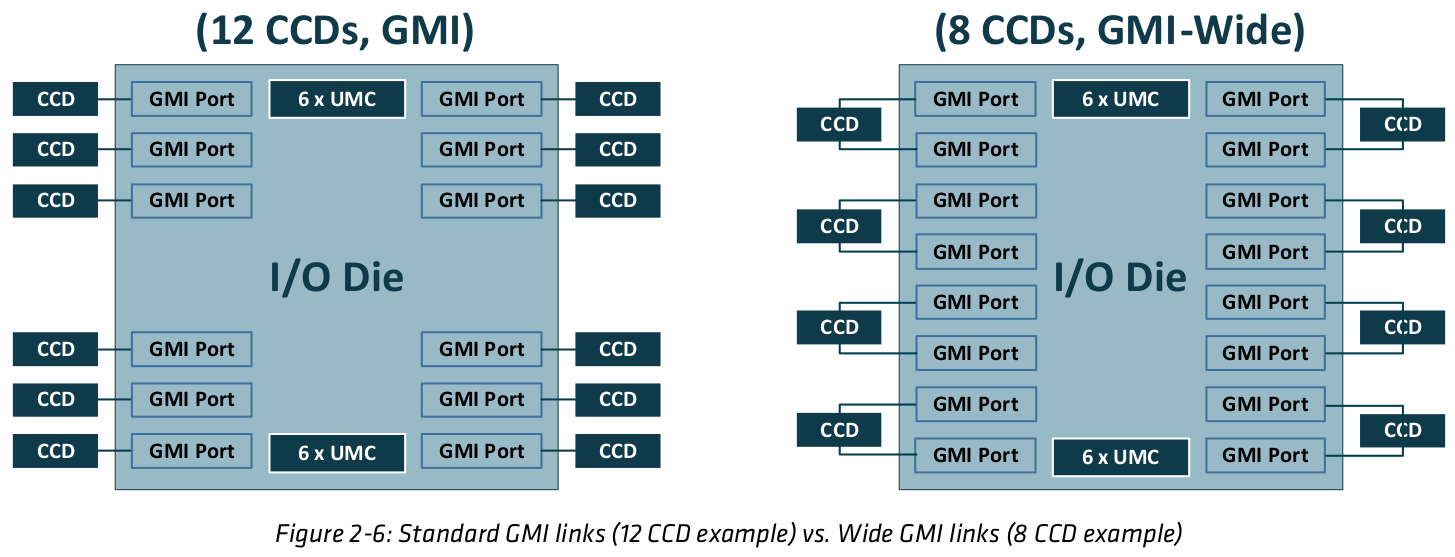

AMD还提供“宽”OPN,其中每个CCD连接到两个GMI接口,从而使核心到I/O芯片带宽翻倍。

IOD提供最多12个支持DDR5内存的统一内存控制器(UMC)。IOD还提供4个“P-link”,系统OEM/平台设计人员可以配置这些P-link以支持各种I/O接口,例如PCIe Gen5和/或CXL 2.0。

内存、I/O和连接

每个UMC每通道(DPC)最多可支持2个DIMM,每个插槽最多可支持24个DIMM。OEM服务器配置可能允许每通道1个DIMM或每通道2个DIMM。第五代AMD EPYC处理器最多可支持9 TB的DDR5内存。与前几代AMD EPYC处理器相比,拥有更多更快的内存通道可提供额外的内存带宽来满足高核心数处理器的需求。2DPC配置可以提供最大内存容量,而1DPC配置可以提供更低的延迟。跨通道内存交错有助于优化各种工作负载和内存配置。

每个处理器可能有一组4个P链路和4个G链路。OEM主板设计可以使用G链路连接到第二个第五代AMD EPYC处理器或提供额外的PCIe Gen5通道。单个第五代AMD EPYC处理器支持最多八组x16位I/O通道,即单插槽平台中的128条高速PCIe Gen5通道和双插槽平台中的160条通道。此外,OEM可以将这128条通道中的32条配置为SATA通道,也可以将64条通道配置为CXL 2.0。总之,这些处理器可以支持:

- 2P设计中最多4个AMD Infinity Fabric连接的G链路。

- 1P设计中最多8个x16位(128条通道)的PCIe Gen 5外围设备连接(2插槽设计中最多160条通道)。

- 最多64条通道(4个P链路)可专用于Compute Express Link (CXL) 2.0连接到扩展内存。

- 最多32个I/O通道,可配置为SATA磁盘控制器。

第3章:NUMA拓扑

AMD EPYC 9005系列处理器使用非统一内存访问(NUMA)架构,根据处理器核心与内存和I/O控制器的接近程度,可能存在不同的延迟。使用同一NUMA节点内的资源可提供统一的良好性能,而使用不同节点中的资源会增加延迟。

NUMA设置

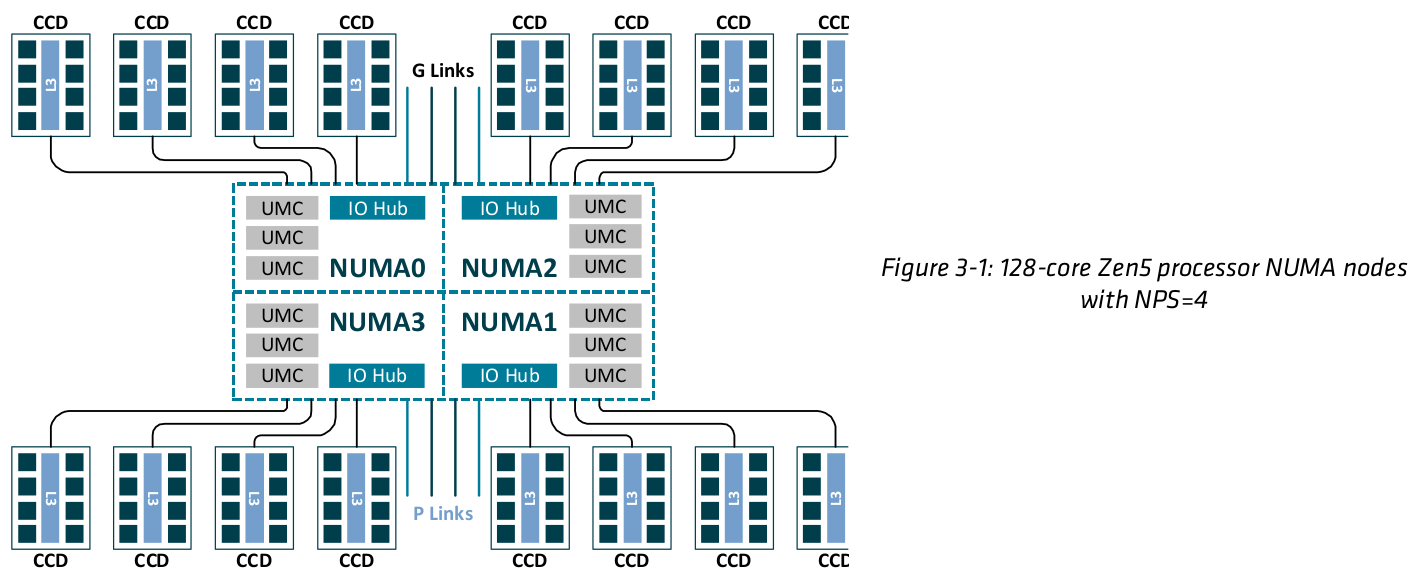

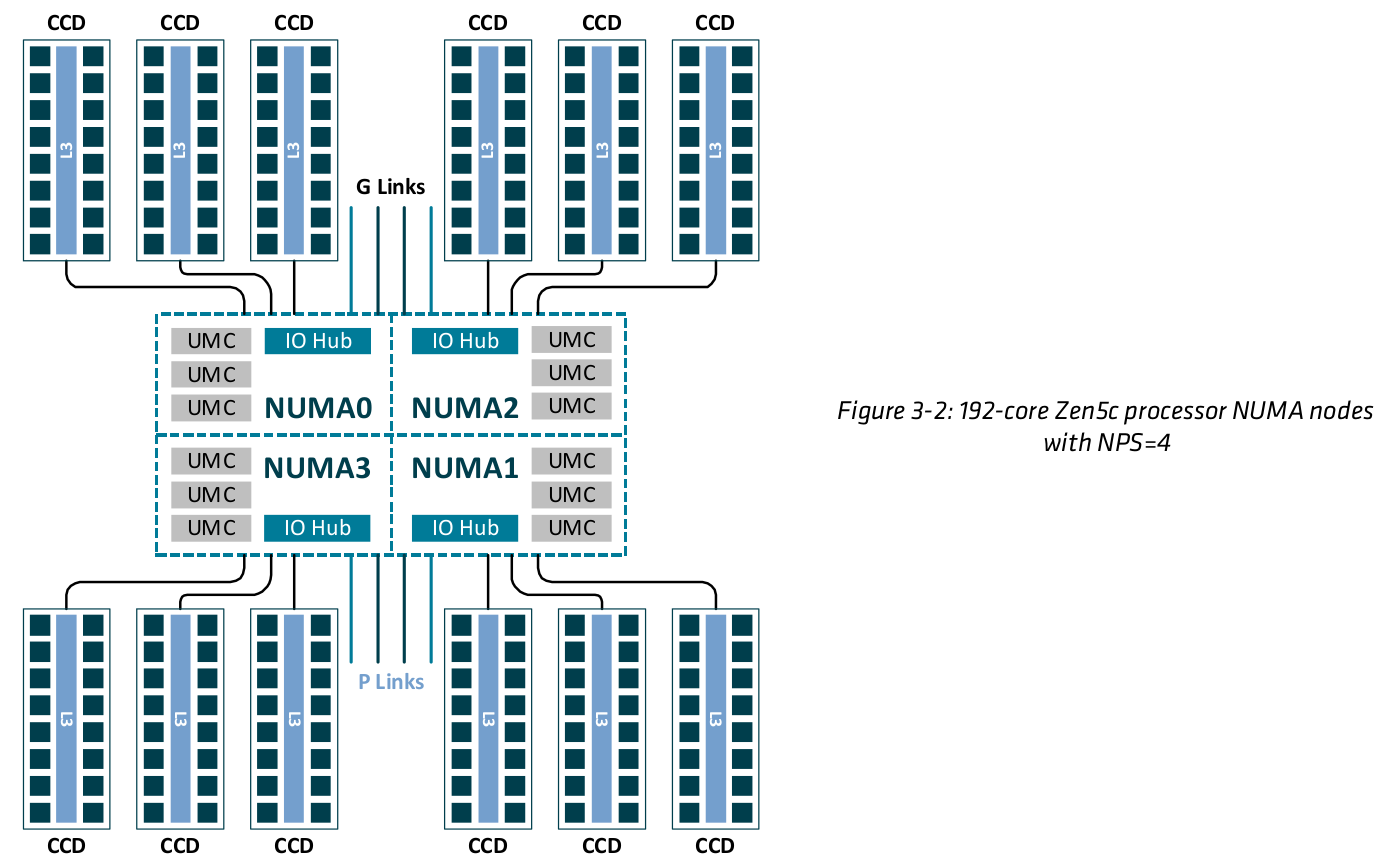

用户可以调整系统NUMA每插槽节点数(NPS) BIOS设置,以针对其特定操作环境和工作负载优化NUMA拓扑。例如,设置NPS=4会将处理器划分为象限,其中每个象限最多有4个CCD、3个UMC和相应的I/O控制器集线器(参见图3-1)。最近的处理器-内存I/O距离是同一象限内的核心、内存和I/O外设之间。最远距离是交叉对角象限中的核心和内存控制器或IO集线器之间的距离(或2P配置中的另一个处理器)。在基于NUMA的系统中,核心、内存和IO集线器/设备的位置是性能调整时的一个重要因素。

NPS设置还控制NUMA节点内内存通道的交错模式。给定NUMA节点内的每个内存通道都是交错的。交错的通道数随着NPS设置变得更加精细而减少。例如,在1P系统上:

- NPS=4的设置将处理器划分为每个插槽四个NUMA节点,每个逻辑象限配置为其自己的NUMA域。内存交错在与每个象限关联的内存通道上。PCIe设备将位于四个处理器NUMA域之一的本地,具体取决于具有该设备对应的PCIe根复合体的IOD象限。

- NPS=2的设置将每个处理器配置为两个NUMA域,将一半的核心和一半的内存通道分组到一个NUMA域中,将剩余的核心和内存通道分组到第二个NUMA域中。内存交错在每个NUMA域中的六个内存通道上。PCIe设备将本地于两个NUMA节点之一,具体取决于具有该设备的PCIe根复合体的一半。

- 设置NPS=1表示每个插槽一个NUMA节点。此设置将处理器上的所有内存通道配置为单个NUMA节点。所有处理器核心、所有连接的内存和连接到SoC的所有PCIe设备都位于该NUMA节点中。内存在处理器上的所有内存通道中交错到单个地址空间中。

- 设置NPS=0表示整个系统的单个NUMA域(在双插槽配置中跨两个插槽)。此设置将系统上的所有内存通道配置为单个NUMA节点。内存在系统上的所有内存通道中交错到单个地址空间中。所有插槽上的所有处理器核心、所有连接的内存和连接到任一处理器的所有PCIe设备都位于该NUMA域中。

您还可以通过使用LLC(L3缓存)作为NUMA BIOS设置将工作负载关联到共享单个LLC的计算核心,从而进一步提高某些环境的性能。启用此设置将每个共享的L3或CCX等同于单独的NUMA节点,作为每个CCD的唯一L3缓存。因此,单个EPYC 9005系列处理器可以支持各种NUMA配置,范围从每个插槽1到16个NUMA节点。

注意:如果软件需要了解NUMA拓扑或核心枚举,则必须使用记录的操作系统(OS) API、定义明确的接口和命令。不要依赖过去对APICID或CCX排序等设置的假设。

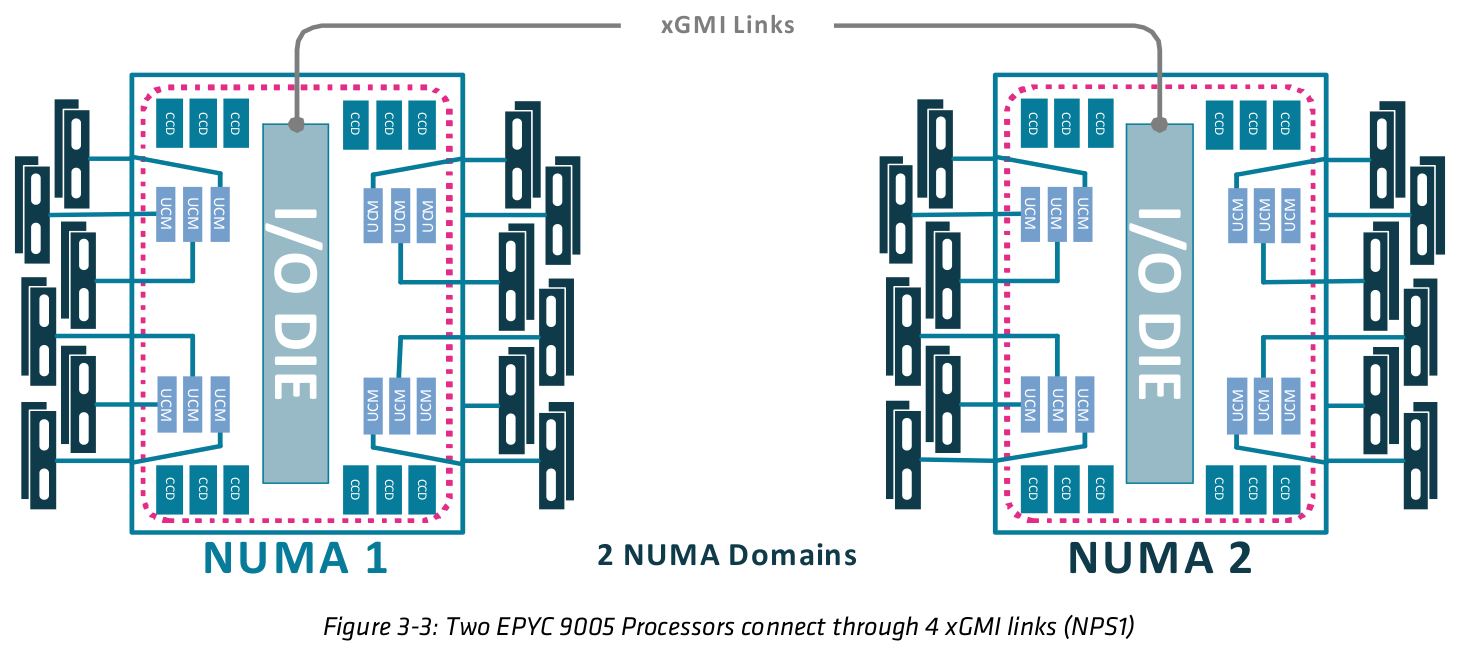

双插槽配置

AMD EPYC 9005系列处理器支持单插槽或双插槽系统配置。名称中带有“P”后缀的处理器仅针对单插槽配置进行了优化(请参阅“处理器标识”一章)。双插槽配置要求两个处理器完全相同。您不能在单个双插槽系统中使用两个不同的处理器订购部件号(OPN)。

在双插槽系统中,两个相同的EPYC 9005系列SoC通过其相应的外部全局内存互连[xGMI]链路连接。这在两个处理器之间创建了高带宽、低延迟互连。系统制造商可以根据I/O和带宽需求以及系统设计目标选择使用3个或4个xGMI/Infinity Fabric链路。

xGMI/Infinity Fabric链路使用与系统上的PCIe通道相同的物理连接。每个链路最多使用16个PCIe通道。典型的双插槽系统将从每个插槽重新配置64个PCIe通道(4个链路)以用于Infinity Fabric连接。这样每个插槽就有64个剩余的PCIe通道,这意味着系统总共有128个PCIe通道。在某些情况下,系统设计人员可能希望通过将Infinity Fabric G-Link的数量从4个减少到3个,为系统提供更多PCIe通道。在这些情况下,设计人员可以为PCIe分配最多160个通道(每个插槽80个),每个插槽仅使用48个通道(而不是64个)用于Infinity Fabric链路。

双插槽系统总共有24个内存通道,或每个插槽12个。可以配置不同的OPN来支持各种NUMA域。

第4章:处理器识别

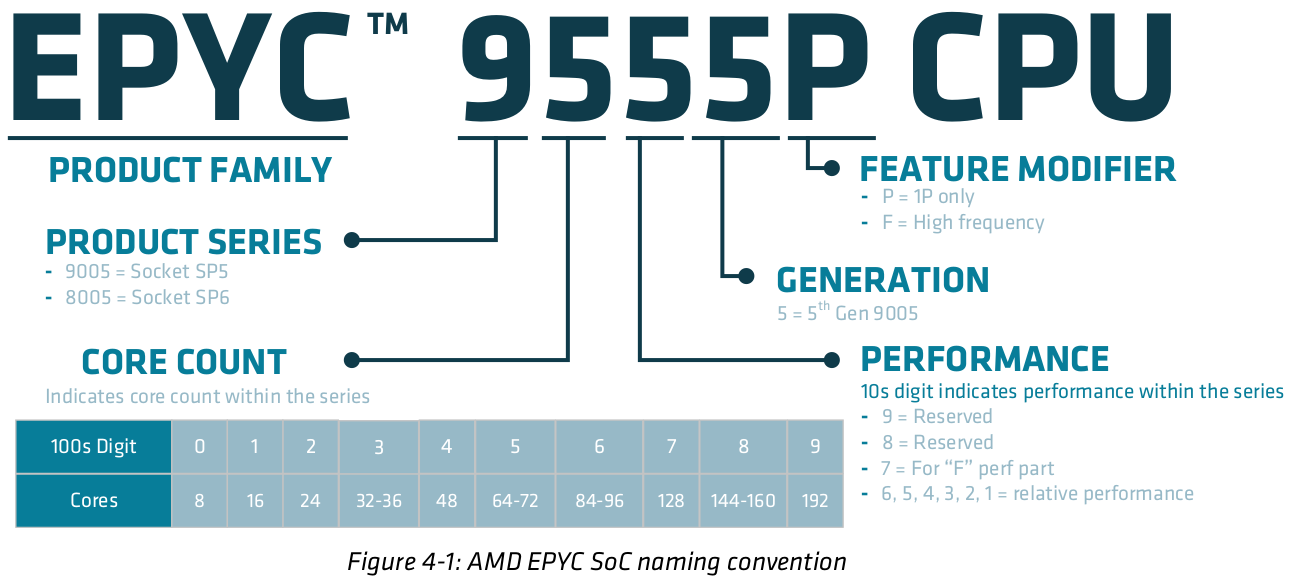

图4-1显示了AMD EPYC 9005系列处理器的处理器命名约定以及如何使用此约定来识别特定的处理器型号:

CPUID指令

软件使用CPUID指令(Fn0000_0001_EAX)来识别处理器,并将返回以下值:

- 系列:1Ah标识“Zen 5”架构。

- 型号:因产品而异。例如,EPYC型号10h对应于“A”部分“Zen 5”CPU。系列

- 步进:可用于进一步识别微小的设计更改。

例如,系列、型号和步进(十进制)的CPUID值25、17、1对应于“B1”部分“Zen 5”CPU。

第5章:其他信息

AMD EPYC 9005系列处理器引入了多项可增强性能的新功能。与上一代AMD EPYC处理器相比,第五代AMD EPYC处理器还包括ISA更新、额外的安全功能以及改进的系统可靠性和可用性。另请参阅最新版本的AMD64架构程序员手册或处理器编程参考(可通过 AMD DEV HUB 获得;长期必需),以了解您的AMD EPYC处理器的相应型号和步进。

并非所有操作系统或虚拟机管理程序都支持所有功能。请参阅您的操作系统或虚拟机管理程序文档以了解特定版本是否支持这些功能。

– AVX-512

第五代AMD EPYC处理器包括具有完整512位路径和寄存器支持的高级矢量扩展(即单指令、多数据[SIMD])操作。第五代AMD EPYC处理器还支持新的VP2INTERSECT指令。hardware – 这篇文章属于一个选集。