计算互连链接(Compute Express Link,CXL)是一种新兴的互连技术,正逐渐成为连接处理器、I/O资源、内存资源以及数据中心和超大规模数据中心中存储设备的主流架构。随着人工智能技术的迅速发展,对大规模数据集的需求不断增加,CXL通过利用标准化的PCIe总线,简化了系统集成过程,这促进了其在嵌入式系统中的广泛应用。

此外,随着汽车行业开始采用数据中心技术,CXL技术有望被整合到下一代汽车中。CXL支持混合资源部署,能够满足复杂系统的需求,并为终端用户提供灵活的资源配置选项。

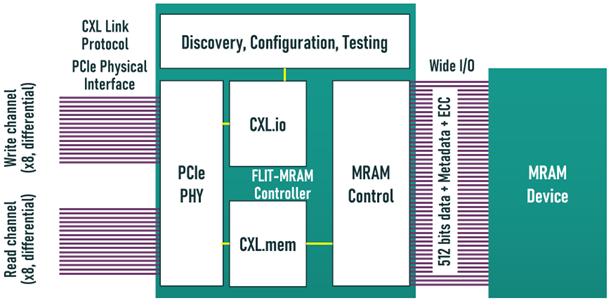

FLIT-MRAM是一种特殊的内存组件,它在CXL的“类型3”模式(CXL.io和CXL.mem)下运行,为新兴的CXL应用提供了独特的非易失性内存解决方案。FLIT-MRAM不仅支持I/O事务,用于设备发现、配置、遥测数据收集和扩展操作,还支持直接内存访问。与传统的行业标准接口(如LPDDR)相比,FLIT-MRAM采用低引脚数接口,提供了更高的性能和更低的功耗,同时确保了数据持久性。这使得FLIT-MRAM成为计算系统中一种理想的解耦持久内存解决方案。

CXL内存的挑战

CXL内存扩展技术正在满足人工智能应用和其他内存密集型计算程序对大容量高性能内存的需求。然而,CXL模块和DRAM内存扩展的应用面临以下几个问题:

- DRAM的易失性及电源故障风险:DRAM在断电时会丢失数据,这可能导致正在进行的操作随时面临风险。

- DRAM的服务质量:访问DRAM时需要考虑刷新操作带来的中断。

针对上述问题,FLIT-MRAM为CXL内存扩展提供了一种独特的解决方案。

DRAM易失性的挑战

DRAM内存单元本质上是一个电容器,通过电荷状态来表示数据位。一旦断电,DRAM会立即丢失所有存储的数据。这一固有弱点长期以来影响着计算机系统的设计。为了应对这一问题,内存层次结构必须包含非易失性存储资源,如SSD,以在断电时永久保存数据。这种从DRAM到SSD的数据检查点保存操作通常会消耗系统约7%的性能和功耗。

自旋转移力矩(STT)磁阻随机存取存储器(MRAM)是一种非易失性内存技术。它利用自旋转移力矩效应,通过极化电流操控电子自旋,在磁性隧道结(MTJ)中建立特定的磁状态,从而表示内存单元的二进制1和0。这种状态在断电时能够保持,电力恢复后数据立即可用。MRAM的这一特性将DRAM和NAND的优势相结合,极大地简化了系统架构,减少了不必要的数据移动,包括检查点保存操作。由于无需多次访问速度较慢的SSD资源来重建数据库,系统恢复时间可以显著缩短。

FLIT-MRAM是一种基于流控制单元(FLIT)的解决方案。CXL FLITs是包含64字节(512位)数据的数据包,与处理器缓存行的自然大小相匹配。因此,具有512位宽内存端口的MRAM核心能够在每个时钟周期传输一个FLIT。这种设计降低了所需的时钟频率,减少了功耗,提高了效率。FLIT-MRAM采用宽I/O内存设备设计,具有集中的内存控制逻辑,将通常分散在多个设备上的功能整合到单一设备中。

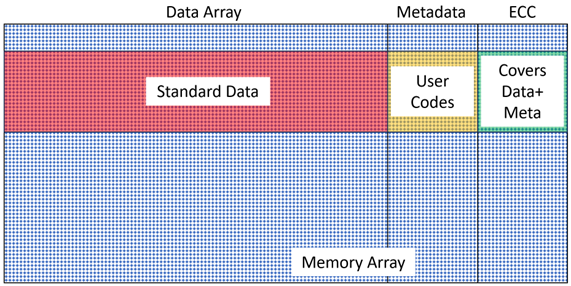

元数据是计算机内存设计中的一个重要话题。元数据允许系统存储关于内存区域的“隐藏”信息,而对元数据的需求量正在不断增加。FLIT-MRAM支持增加受ECC代码保护的元数据位数,每增加一位元数据仅使芯片面积增加0.2%。这使客户能够根据应用需求灵活定义所需的元数据位数。FLIT-MRAM能够以仅6.4%的芯片面积增加量支持强大的三位错误校正方案,相比多设备解决方案,以更低的成本提供了更好的数据保护。

内存确定性的挑战

DRAM控制器包含“刷新”功能,每秒需要对每个位进行超过30次的重新充电。这一刷新过程占用了可用内存传输带宽的4.5%。在85-95°C的高温环境下,这一损耗甚至会增加到9%。相比之下,FLIT-MRAM不需要刷新操作,从而提高了内存接口的确定性,改善了应用程序的服务质量(QoS)。

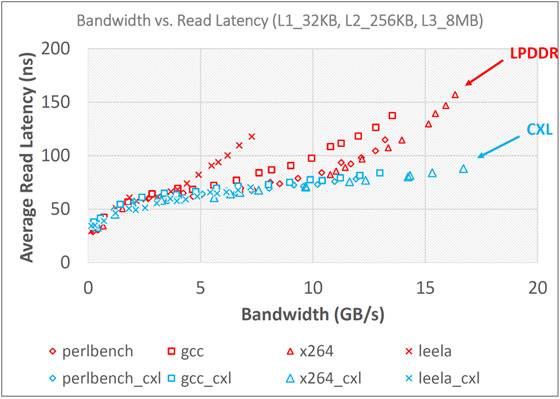

CXL在另一方面与传统内存接口有所不同,这种差异影响了服务质量:CXL支持全双工操作,允许同时进行读写操作。相比之下,传统的DRAM接口,例如双倍数据率(DDR),采用的是半双工模式:从读取切换到写入并返回需要插入延迟时间“气泡”,这会影响性能和服务质量。图1展示了FLIT-MRAM与低功耗DDR(LPDDR)内存的比较。在图的左下角,轻负载应用下,CXL接口的延迟使得LPDDR略占优势。然而,随着应用负载的加重,例如在多核处理器的典型情况下,LPDDR的半双工特性成为主导因素,导致访问时间显著增加。FLIT-MRAM利用CXL的全双工特性来掩盖这些缺点,即使在重负载下也能保持更稳定的性能。

通用加速

CXL提供了一项重要功能:基于PCIe接口的CXL.io协议。该通道支持DDR无法实现的命令,如执行内存填充操作。CXL.io通道允许随时间添加多种新功能,包括压缩、加密、内存中处理等,这些可以纳入产品路线图或定制解决方案中。

FLIT-MRAM在人工智能中的应用

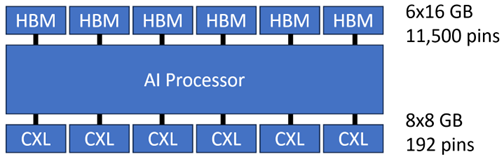

FLIT-MRAM为AI解决方案提供了简单的扩展机制,并充分利用其非易失性特性。它不需要替代所有AI内存(如用于存储数据集的HBM),而是可作为HBM的补充,允许应用程序将“检查点”数据分区到FLIT-MRAM中,从而在断电时提供数据恢复能力。FLIT-MRAM仅需32个有效信号,且允许与处理器之间有100毫米的距离,可用于增加总内存容量并消除检查点保存。每个FLIT-MRAM可独立运行,不使用时可进入深度休眠或关闭以节省功耗。

FLIT-MRAM在汽车应用中的应用

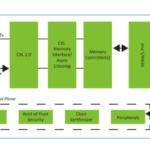

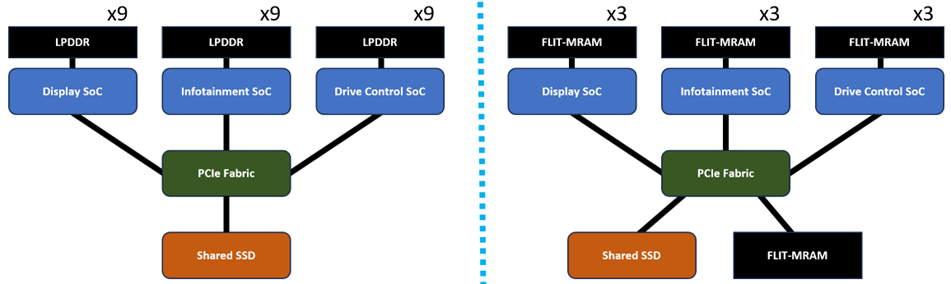

随着汽车联网程度提高、传感器和控制系统集成增加、多个高清显示器管理需求增长以及AI能力增强,汽车电子设备已演变为关键的数据中心应用。汽车电子设计正向PCIe迁移,作为连接多个高性能系统芯片(SoC)处理器的结构。典型SoC使用九个LPDDR DRAM,采用144位数据总线,无共享内存。可能的系统重新设计方案是用三个FLIT-MRAM替代九个LPDDR设备,并可选择在PCIe结构中添加更多共享内存资源,简化处理器间的数据传输。采用FLIT-MRAM作为内存资源的汽车可实现即时启动,这一功能在实际应用中可能挽救生命。

结论

FLIT-MRAM通过利用日益普及的CXL基础设施,重新构思了DRAM解决方案的架构。将DRAM DDRx物理接口替换为CXL接口,使内存事务能够通过CXL的64字节FLIT有效负载与处理器的64字节缓存行匹配。

FLIT-MRAM为处理架构带来了透明的非易失性,提高了服务质量和数据可靠性。

潜在应用包括笔记本电脑、AI加速器、汽车和工业控制系统。甚至服务器主板供应商也越来越多地考虑这种内存扩展形式是否有助于突破内存墙并提高系统性能。